- #Designing median filter using altera dsp builder manual#

- #Designing median filter using altera dsp builder full#

- #Designing median filter using altera dsp builder software#

- #Designing median filter using altera dsp builder Pc#

DSPs are a class of hardware devices that fall somewhere between an ASIC and a PC in terms of the performance and the design complexity. In addition, during design fabrication the presence of a single error renders the chip useless. ASIC designs are used in high volume commercial applications. The ASIC design cannot be changed and the design time is also very high.

#Designing median filter using altera dsp builder full#

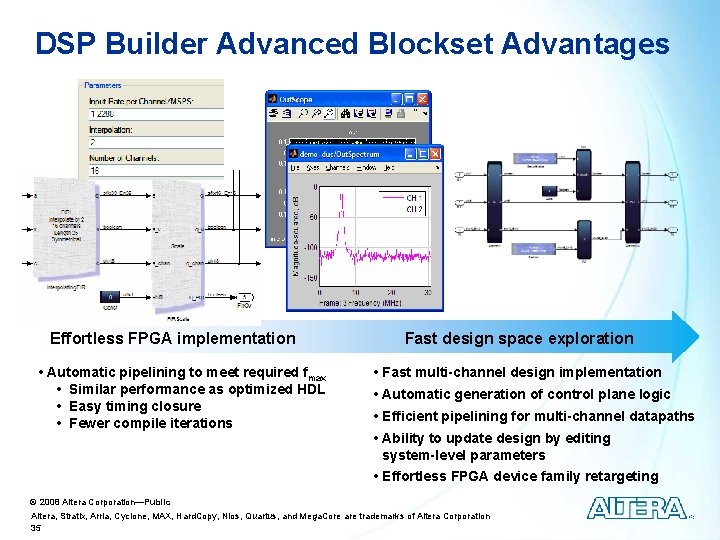

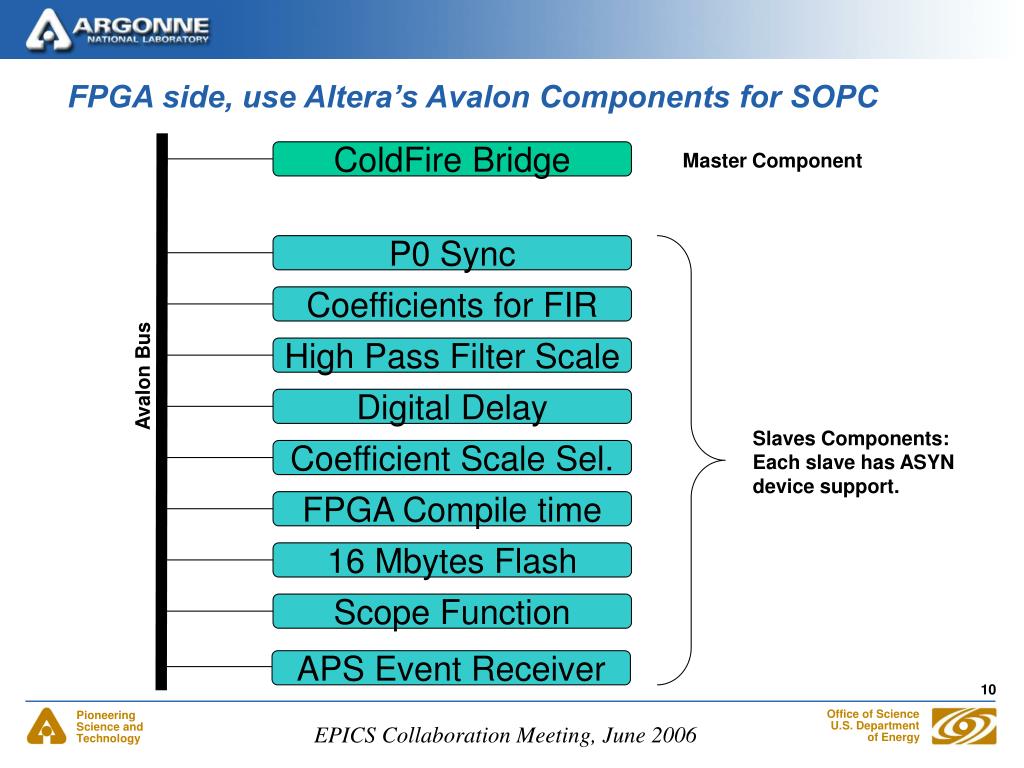

Full custom ASIC design offers highest performance, but the complexity and the cost associated with the design is very high. Full custom hardware design also called as Application Specific Integrated Circuits (ASIC) and semi custom hardware device, which are programmable devices like Digital signal processors (DSPs) and Field Programmable Gate Arrays (FPGAs). There are two types of technologies available for hardware design. Implementing complex computation tasks on hardware and by exploiting parallelism and pipelining in algorithms yield significant reduction in execution times. With advances in the VLSI (Very Large Scale Integrated) technology hardware implementation has become an attractive alternative.

#Designing median filter using altera dsp builder software#

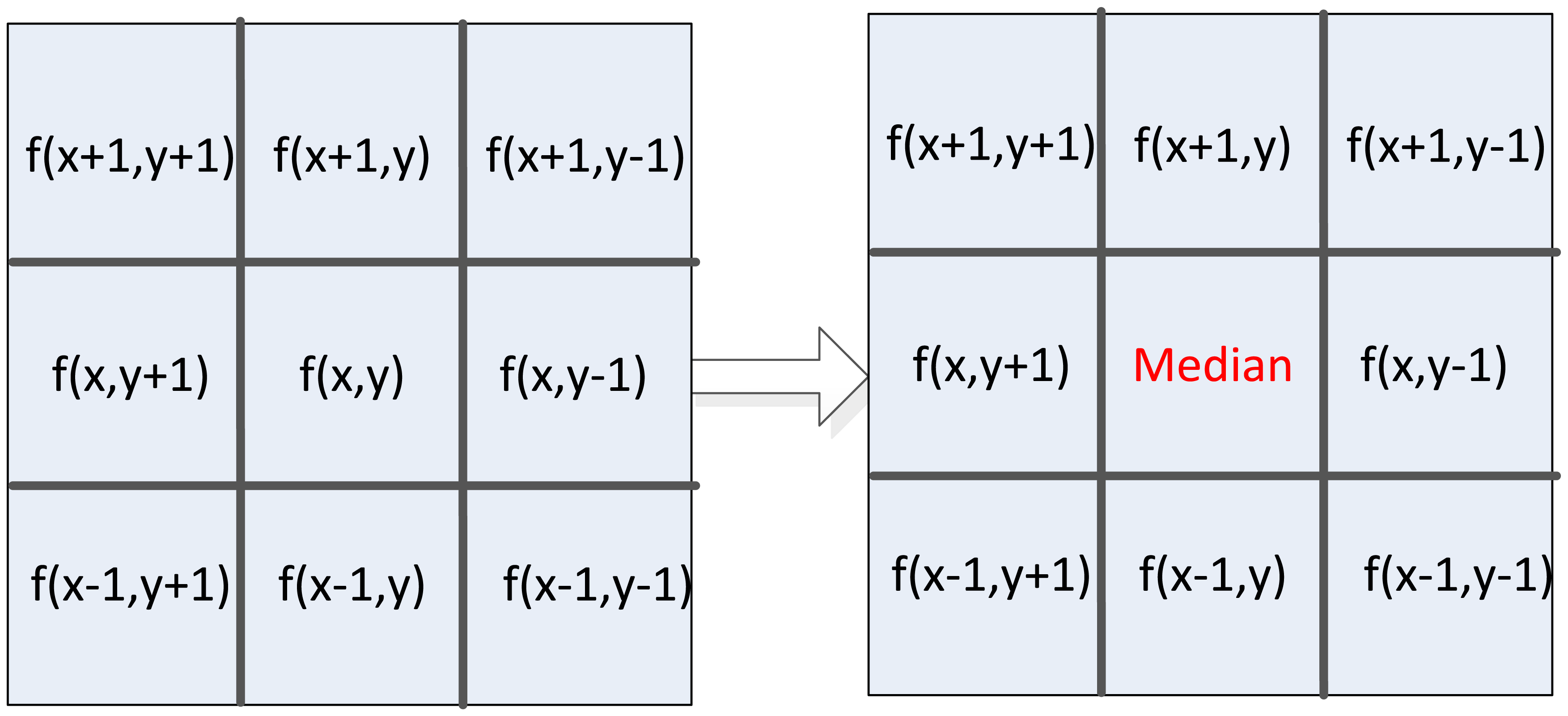

Application specific hardware implementation offers much greater speed than a software implementation. Implementing such applications on a general purpose computer can be easier, but not very time efficient due to additional constraints on memory and other peripheral devices. Applications such as these involve different processes like image enhancement and object detection. A comparison of our architecture for Cannys edge detection with other architecture is also discussed.ĭigital image processing is an ever expanding and dynamic area with applications reaching out into our everyday life such as medicine, space exploration, surveillance, authentication, automated industry inspection and many more areas. The proposed architecture is capable of producing one edge-pixel every clock cycle. The work also proposes a novel hardware architecture to implement Cannys edge detection algorithm. Our evaluations show that the Handel-C implementation perform better at system and synthesis level compared to other languages considered in this work. Comparison parameters at synthesis level include logic resources required, maximum frequency of operation and execution time.

Comparison parameters at simulation level include, man-hours for implementation, compile time and lines of code. The image processing algorithms considered include, image filtering, image smoothing and edge detection. This work evaluates the performance and efficiency of Handel-C language on image processing algorithms and is compared at simulation level with another popular C-based system level language called SystemC and at synthesis level with the industry standard Hardware Descriptive language, provides both simulation and synthesis capabilities. Handel-C language and the IDE tool introduced by Celoxica Ltd. Handel-C is a new C-based language proposed that provides direct implementation of hardware from the C-based language description of the system.

#Designing median filter using altera dsp builder manual#

However, the synthesis process of the system to hardware was not completely addressed and was conducted using manual methods resulting in duplication of the implementation process. These languages have greatly simplified the task of designing and verifying hardware implementation of the system. In order to overcome this bottleneck various C-based hardware descriptive languages have been proposed over the past decade. Most of the system level hardware programming languages introduced and commonly used in the industry are highly hardware specific and requires intermediate to advance hardware knowledge to design and implement the system.

The introduction of reconfigurable devices and system level hardware programming languages has further accelerated the design of image processing in hardware. Image Processing algorithms implemented in hardware have emerged as the most viable solution for improving the performance of image processing systems. Las Vegas, NV 89154 *E-mail: the advent of mobile embedded multimedia devices that are required to perform a range of multimedia tasks, especially image processing tasks, the need to design efficient and high performance image processing systems in a short time-to-market schedule needs to be addressed. Implementation and Evaluation of Image Processing Algorithms on Reconfigurable Architecture usingĭaggu Venkateshwar Rao*, Shruti Patil, Naveen Anne Babu and V Muthukumarĭepartment of Electrical and Computer Engineering University of Nevada Las Vegas. 934 (c) GBS Publishers and Distributors (India) International Journal of Theoretical and Applied Computer Sciences Volume 1 Number 1 (2006) pp.

0 kommentar(er)

0 kommentar(er)